# Smartcoder (AU6805)

## **USERS MANUAL**

|       |                                                                                                          |         |        |      | 改    | 訂      |      | 来  | 歴 |       |   |                 |       |        |       |

|-------|----------------------------------------------------------------------------------------------------------|---------|--------|------|------|--------|------|----|---|-------|---|-----------------|-------|--------|-------|

| 訂正番号  | 年月日                                                                                                      | ~~ -    | ジ      |      |      | 改      | 訂    | 理  | 由 |       |   | 作员              | ţ,    | 京検     | 承認    |

|       |                                                                                                          |         |        |      |      |        |      |    |   |       |   |                 |       |        |       |

|       |                                                                                                          |         |        |      |      |        |      |    |   |       |   |                 |       |        |       |

|       |                                                                                                          |         |        |      |      |        |      |    |   |       |   |                 |       |        |       |

|       |                                                                                                          |         |        |      |      |        |      |    |   |       |   |                 |       |        |       |

|       |                                                                                                          |         |        |      |      |        |      |    |   |       |   |                 |       |        |       |

|       |                                                                                                          |         |        |      |      |        |      |    |   |       |   |                 |       | /      |       |

|       |                                                                                                          |         |        |      |      |        |      |    |   |       |   |                 |       |        |       |

|       |                                                                                                          |         |        |      |      |        |      |    |   |       |   |                 |       |        |       |

|       |                                                                                                          |         |        |      |      |        |      |    |   |       |   |                 |       |        |       |

|       |                                                                                                          |         |        |      |      |        |      |    |   |       |   | ED'N            | N No. |        |       |

| DS' I |                                                                                                          |         | DATE   | 3    | MODI | EL No. |      |    |   | TITLE |   |                 | I /AI | 1000E) |       |

| GIII  | H. Mar                                                                                                   | uyainil | 7      | 3.30 |      | А      | .U68 | 05 |   |       |   | artcod<br>ISERS |       |        |       |

| CH' I | K. Ishi                                                                                                  | loski   | DWG NO | ).   | 3    | 4      | 5    | 6  | 7 | 8     | 9 | 10              | 11    | 12     | SHEET |

| APP'  | CH' $\Gamma$ N. Alshilashi DWG NO. 3 4 5 6 7 8 9 10 11 12 SHEET MN N L O O O 6 3 4 W O O $\frac{0}{108}$ |         |        |      |      |        |      |    |   |       |   |                 |       |        |       |

# Smartcoder®

AU6805

**USERS MANUAL**

## Table of Contents

| Safety Precautions                                                                  | - 5  | _ |

|-------------------------------------------------------------------------------------|------|---|

| 1. Introduction                                                                     | - 6  | _ |

| 1.1 Product Overview                                                                | - 6  | - |

| 1.2 Product Features                                                                |      |   |

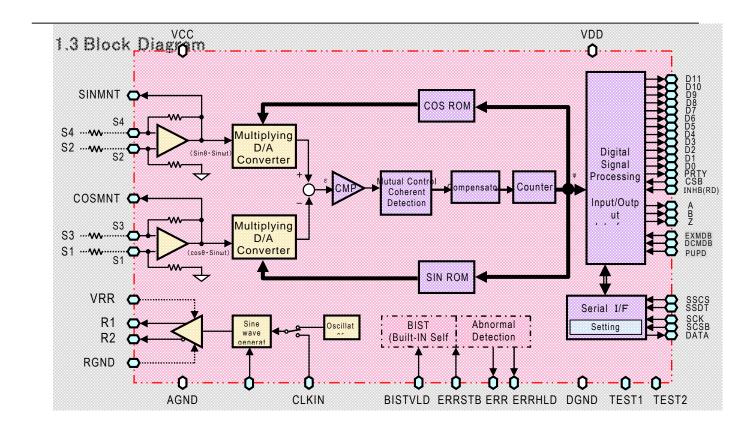

| 1.3 Block Diagram                                                                   |      |   |

| 1.5 Related Documents                                                               |      |   |

|                                                                                     |      |   |

| 2. Pin List (Name and Functions)                                                    |      |   |

| 2.1 Pin Assignment                                                                  |      |   |

| 2.2 Pin Description                                                                 |      |   |

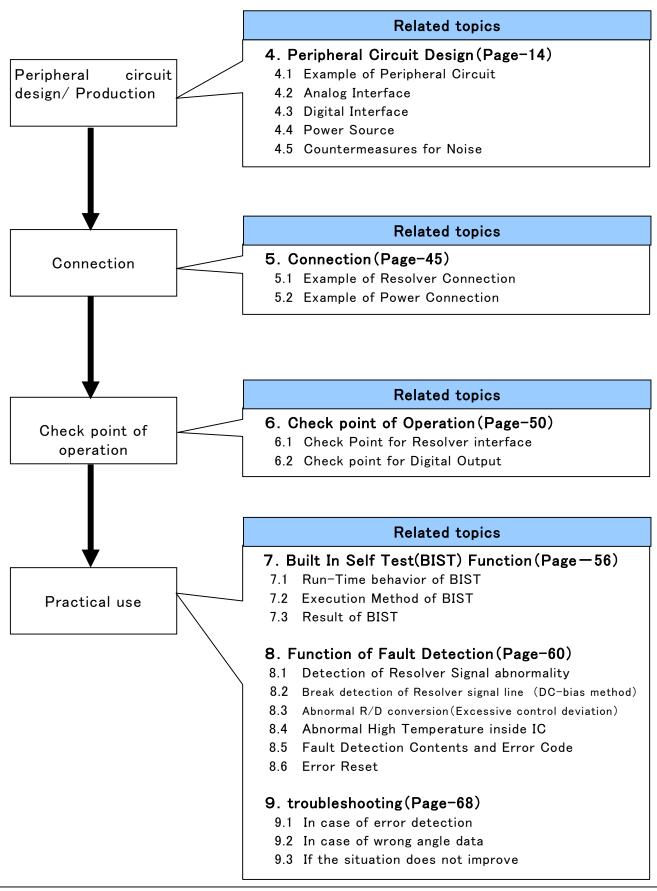

| 3. Setup Flow                                                                       | 13   | _ |

| 4. Peripheral Circuit Design                                                        | 1.1  |   |

|                                                                                     |      |   |

| 4.1 Example of Peripheral Circuit                                                   |      |   |

| 4.2.1 Resolver Excitation Circuit                                                   |      |   |

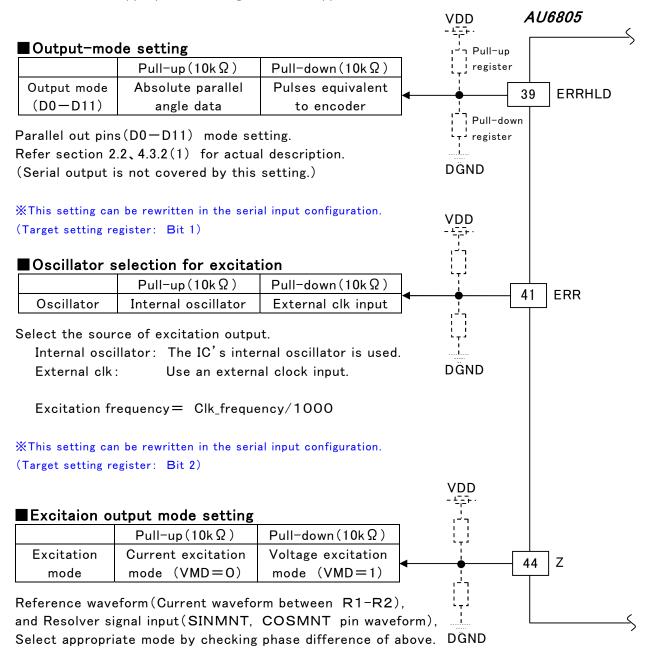

| 4.2.2 Resolver Signal Input Circuit                                                 |      |   |

| 4.2.3 External input circuit for resolver (External excitation case)                |      |   |

| 4.3 Digital Interface                                                               |      |   |

| 4.3.1 Mode Setting*Function Selection                                               |      |   |

| 4.3.3 Clock for Excitation                                                          |      |   |

| 4.4 Power Source                                                                    |      |   |

| 4.5 Countermeasures for Noise                                                       | - 44 | - |

| 5. Connection                                                                       | 45   | _ |

| 5.1 Example of Resolver Connection                                                  |      |   |

| 5.2 Example of Power Connection –                                                   |      |   |

| 6. Check Point of Operation                                                         | 50   | _ |

| 6.1 Check Point for Resolver Interface                                              |      |   |

| 6.1.1 Check Point for Resolver Interrace – 6.1.1 Check Point of Excitation Signal – |      |   |

| 6.1.2 Check Point of Monitor Signal Amplitude                                       |      |   |

| 6.1.3 Check Point of Phase Shift                                                    | 51   | - |

| 6.2 Check Point for Digital Output                                                  |      |   |

| 6.2.1 Check Point of Output Angle 6.2.2 Check point of abnormality Detection        |      |   |

|                                                                                     |      |   |

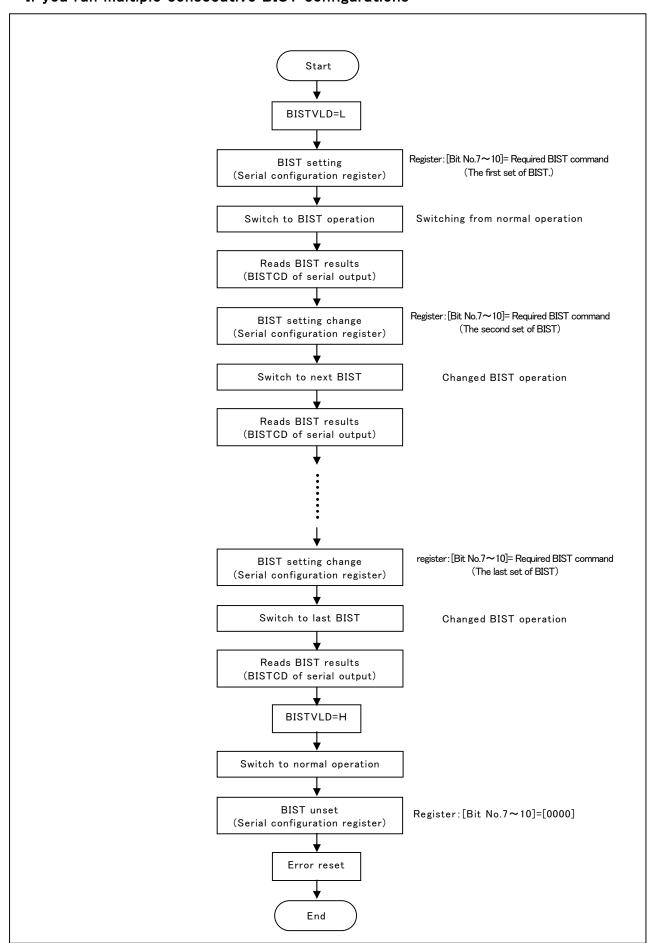

| 7. Built In Self Test(BIST)Function                                                 |      |   |

| 7.1 Run-Time Behavor of BIST                                                        |      |   |

| 7.2 Execution Method of BIST                                                        |      |   |

| 7.3 Result of BIST                                                                  | 59   | _ |

| 8. Function of Fault Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | – 60 –                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.1 Abnormal Resolver Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 60 -                                                                                                                                                                                                     |

| 8.1.1 Concept Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                          |

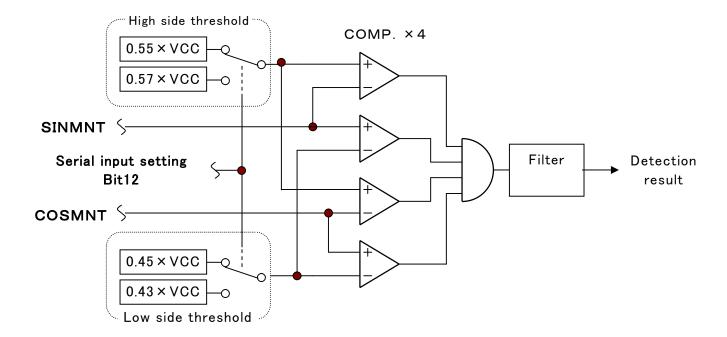

| 8.1.2 Circuit Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60 -                                                                                                                                                                                                     |

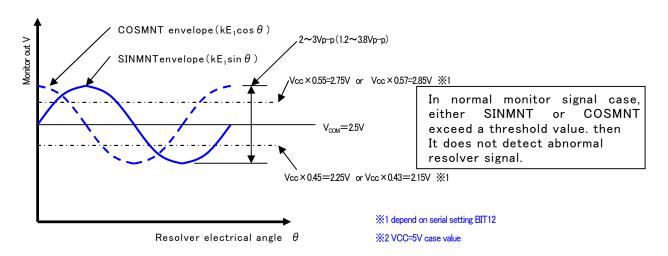

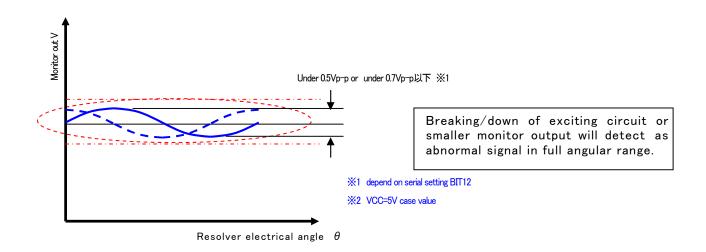

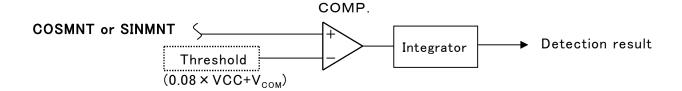

| 8.1.3 Detection Principle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 61 -                                                                                                                                                                                                     |

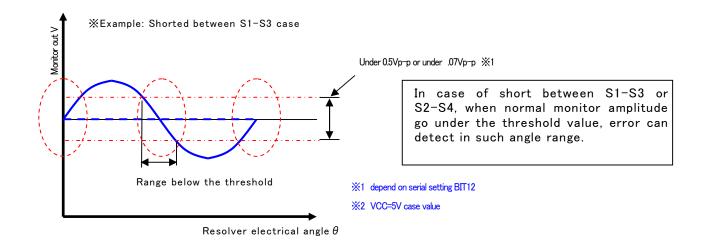

| 8.1.4 Relationship of threshold and Typical abnormal detection pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 61 -                                                                                                                                                                                                     |

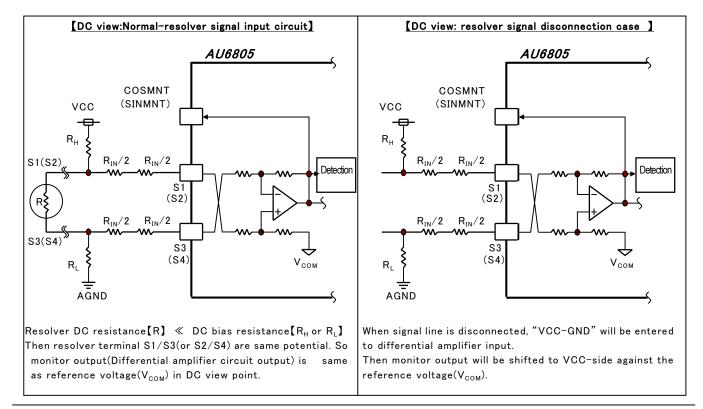

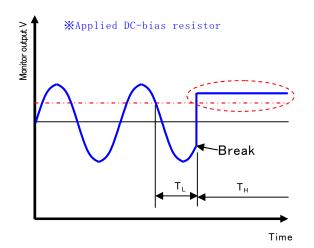

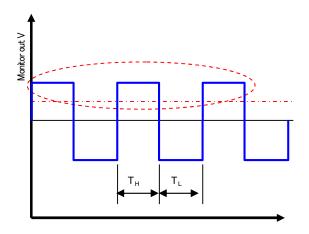

| 8.2 Disconnection of Resolver Signal Line(DC-bias method)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                          |

| 8.2.1 Concept Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                          |

| 8.2.2 Circuit Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                          |

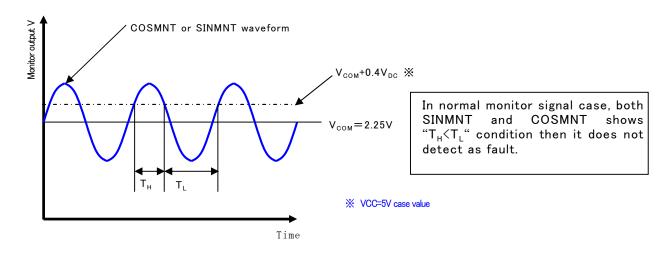

| 8.2.3 Detection Principle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                          |

| 8.2.4 Relationship of threshold and Typical abnormal detection pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |

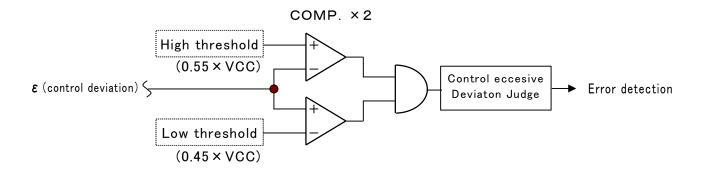

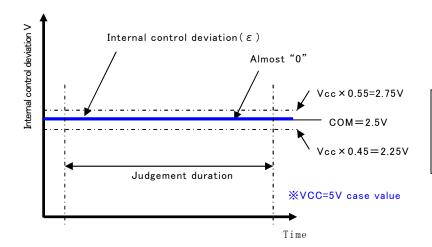

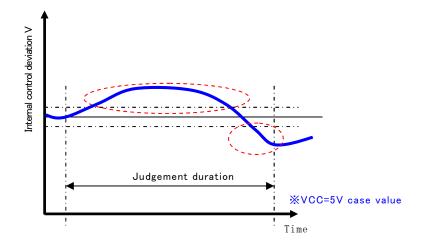

| 8.3 Abnormal R/D conversion(Excessive control deviation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                          |

| 8.3.1 Concept Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                          |

| 8.3.2 Circuit Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                          |

| 8.3.3 Detection Principle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                          |

| 8.3.4 Relationship of threshold and Typical abnormal detection pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |

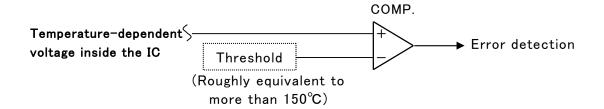

| 8.4 Abnormal High Temperature inside IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                          |

| 8.4.1 Concept Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                          |

| 8.4.3 Detection Principle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                          |

| 8.4.4 Relationship of threshold and Typical abnormal detection pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |

| 8.5 Fault Detection Contents and Error Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                          |

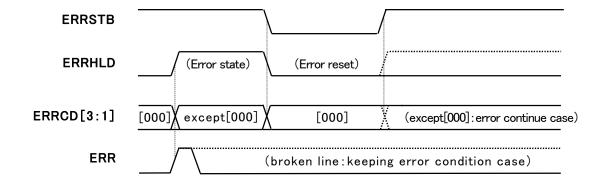

| 8.6 Error Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                          |

| 0.0 Little Neset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 01                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                          |

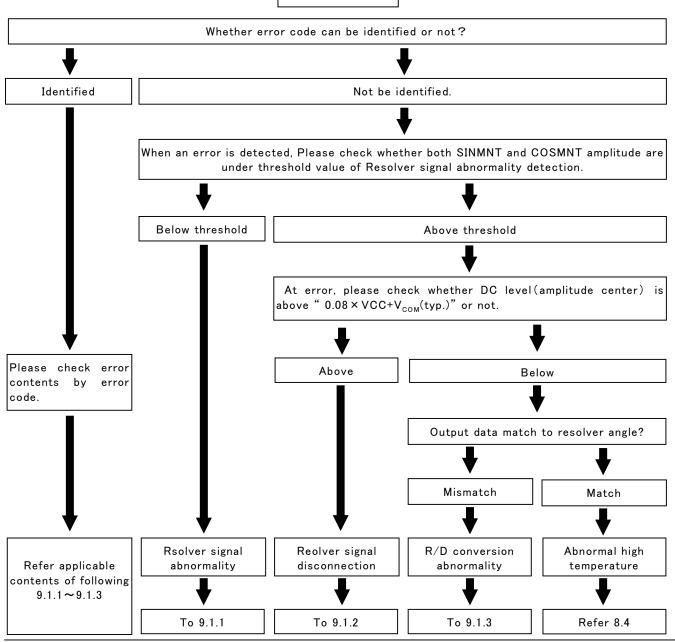

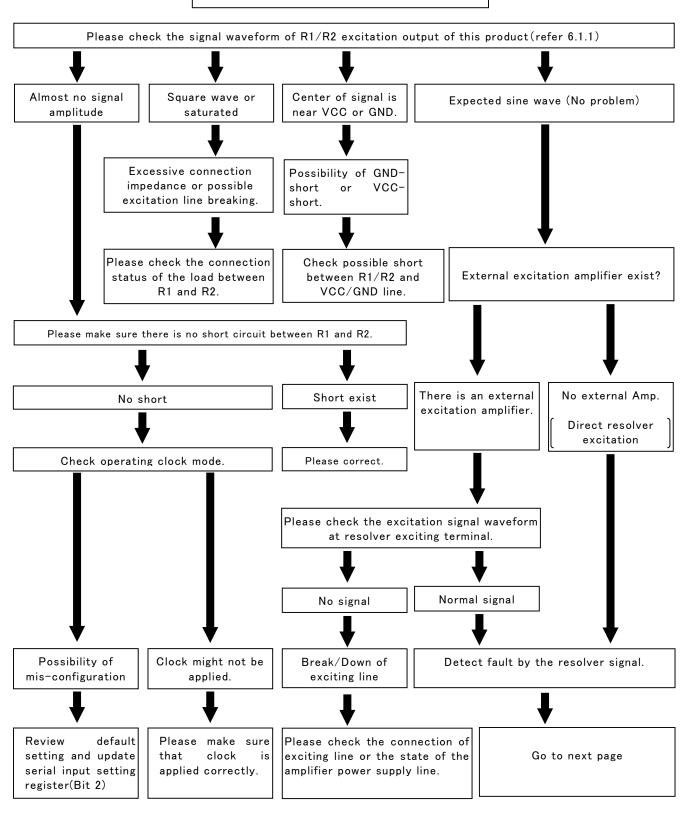

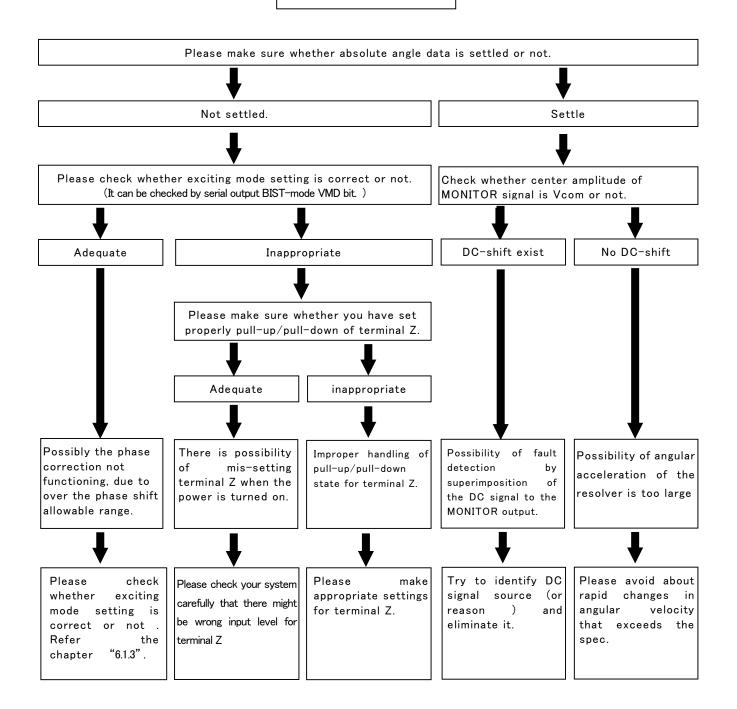

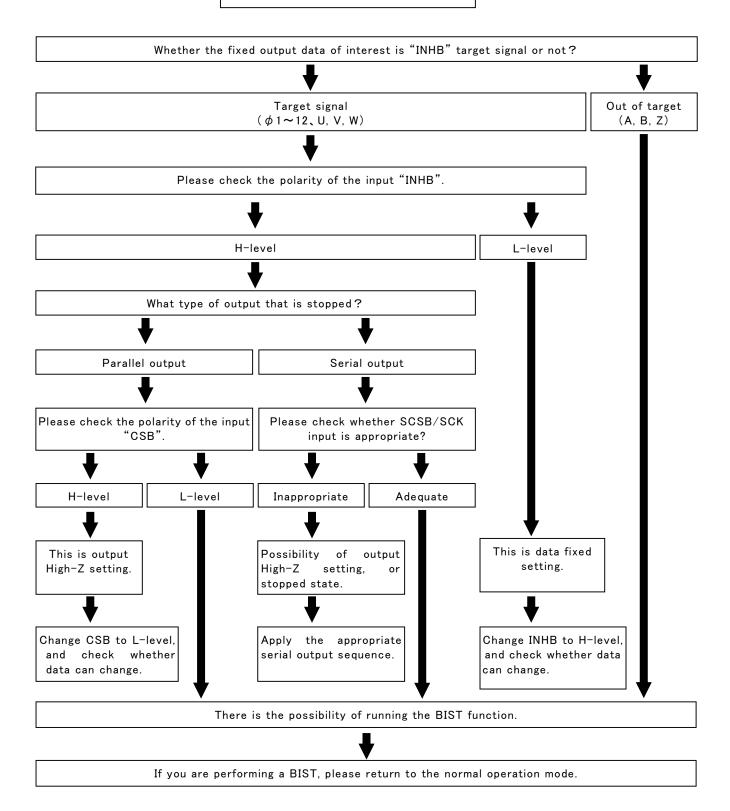

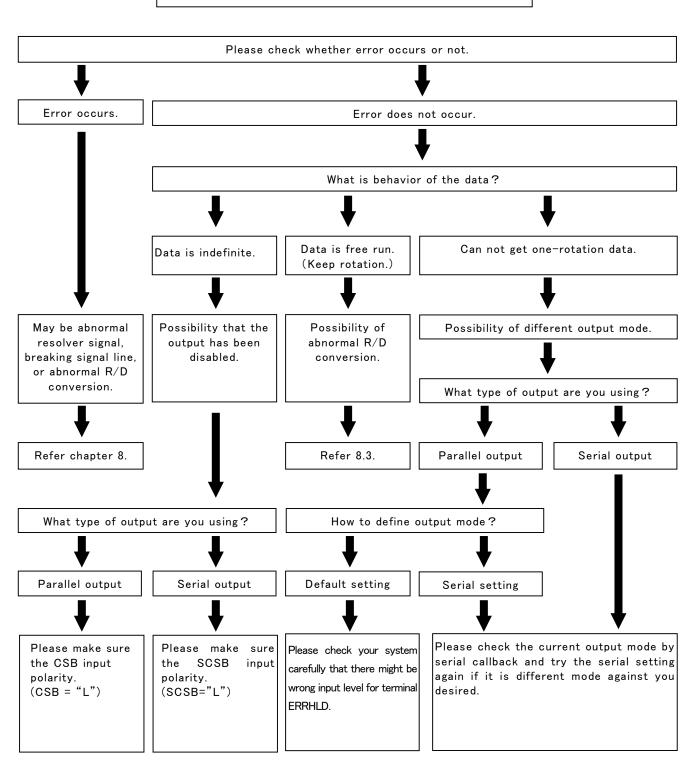

| 9. If you think trouble shooting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68 -                                                                                                                                                                                                     |

| 9. If you think trouble shooting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                          |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 68 -                                                                                                                                                                                                     |

| 9.1 In case of error detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 68 -<br>69 -<br>71 -                                                                                                                                                                                     |

| 9.1 In case of error detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 68 -<br>69 -<br>71 -                                                                                                                                                                                     |

| 9.1 In case of error detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 68 - 69 - 69 - 71 - 72 - 73 - 73 - 73                                                                                                                                                                    |

| 9.1 In case of error detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 68 69 71 72 73 74 -                                                                                                                                                                                      |

| 9.1 In case of error detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 68 - 69 - 69 - 71 - 72 - 72 - 73 - 74 - 75 - 75 - 68 - 75 - 68 - 68 - 68 - 68 - 68 - 68 - 68 - 6                                                                                                         |

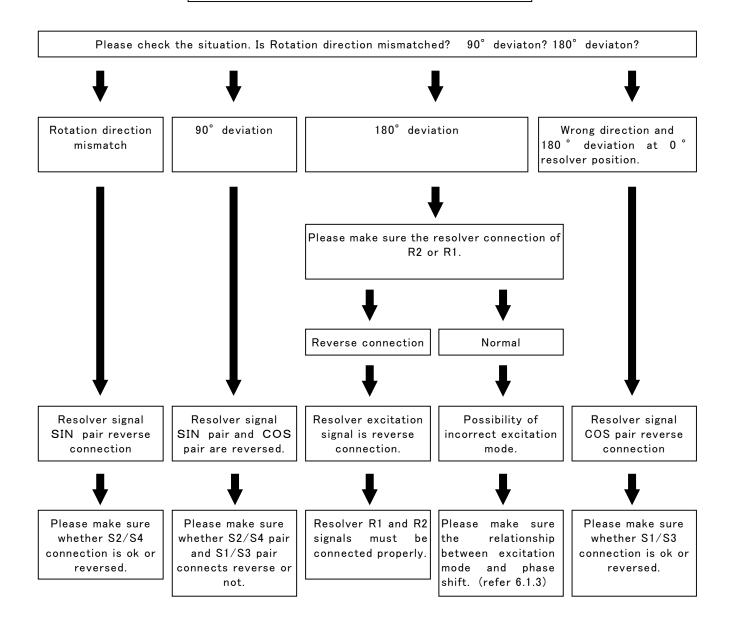

| 9.1 In case of error detection 9.1.1 Suspicion of Abnormal Resolver Signal 9.1.2 Suspicion of Disconnection Detection (DC-bias method) 9.1.3 Suspicion of Abnormal R/D conversion 9.2 In case of wrong angle data 9.2.1 In case of fixed angle data 9.2.2 In case of indefinite, free run, can not get one-rotation data 9.2.3 In case of rotation direction difference, 90° deviation or 180° deviation.                                                                                                                                                                                                                                                                                                                                                                                                                       | 68 69 71 72 73 74 75 76 -                                                                                                                                                                                |

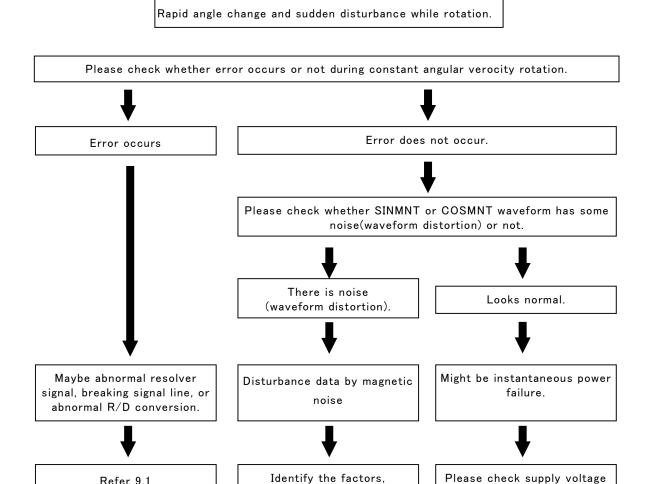

| 9.1 In case of error detection  9.1.1 Suspicion of Abnormal Resolver Signal.  9.1.2 Suspicion of Disconnection Detection (DC-bias method)  9.1.3 Suspicion of Abnormal R/D conversion  9.2 In case of wrong angle data.  9.2.1 In case of fixed angle data  9.2.2 In case of indefinite, free run, can not get one-rotation data.  9.2.3 In case of rotation direction difference, 90° deviation or 180° deviation.  9.2.4 In case of rapid change in the output angle data and disturbance                                                                                                                                                                                                                                                                                                                                     | 68 69 71 72 73 74 75 76 77 -                                                                                                                                                                             |

| 9.1.1 Suspicion of Abnormal Resolver Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 68 69 71 72 73 74 75 76 77 -                                                                                                                                                                             |

| 9.1 In case of error detection 9.1.1 Suspicion of Abnormal Resolver Signal. 9.1.2 Suspicion of Disconnection Detection (DC-bias method) 9.1.3 Suspicion of Abnormal R/D conversion 9.2 In case of wrong angle data. 9.2.1 In case of fixed angle data 9.2.2 In case of indefinite, free run, can not get one-rotation data. 9.2.3 In case of rotation direction difference, 90° deviation or 180° deviation. 9.2.4 In case of rapid change in the output angle data and disturbance. 9.3 If the situation does not improve                                                                                                                                                                                                                                                                                                      | 68 69 71 72 73 74 75 76 77 -                                                                                                                                                                             |

| 9.1 In case of error detection 9.1.1 Suspicion of Abnormal Resolver Signal 9.1.2 Suspicion of Disconnection Detection (DC-bias method) 9.1.3 Suspicion of Abnormal R/D conversion 9.2 In case of wrong angle data 9.2.1 In case of fixed angle data 9.2.2 In case of indefinite, free run, can not get one-rotation data 9.2.3 In case of rotation direction difference, 90° deviation or 180° deviation 9.2.4 In case of rapid change in the output angle data and disturbance 9.3 If the situation does not improve                                                                                                                                                                                                                                                                                                           | 68 69 71 72 73 74 75 76 77 77 -                                                                                                                                                                          |

| 9.1 In case of error detection 9.1.1 Suspicion of Abnormal Resolver Signal. 9.1.2 Suspicion of Disconnection Detection (DC-bias method) 9.1.3 Suspicion of Abnormal R/D conversion 9.2 In case of wrong angle data. 9.2.1 In case of fixed angle data 9.2.2 In case of indefinite, free run, can not get one-rotation data. 9.2.3 In case of rotation direction difference, 90° deviation or 180° deviation. 9.2.4 In case of rapid change in the output angle data and disturbance. 9.3 If the situation does not improve.                                                                                                                                                                                                                                                                                                     | 68 69 71 72 73 74 75 76 77 77 78 -                                                                                                                                                                       |

| 9.1 In case of error detection 9.1.1 Suspicion of Abnormal Resolver Signal. 9.1.2 Suspicion of Disconnection Detection (DC-bias method) 9.1.3 Suspicion of Abnormal R/D conversion 9.2 In case of wrong angle data. 9.2.1 In case of fixed angle data 9.2.2 In case of indefinite, free run, can not get one-rotation data. 9.2.3 In case of rotation direction difference, 90° deviation or 180° deviation. 9.2.4 In case of rapid change in the output angle data and disturbance 9.3 If the situation does not improve.  10. Electrical characteristics  10.1 Absolute maximum rating 10.2 Power-related characteristic.                                                                                                                                                                                                     | 68 69 71 72 73 74 75 76 77 77 77 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 78 |

| 9.1 In case of error detection 9.1.1 Suspicion of Abnormal Resolver Signal. 9.1.2 Suspicion of Disconnection Detection (DC-bias method) 9.1.3 Suspicion of Abnormal R/D conversion 9.2 In case of wrong angle data 9.2.1 In case of fixed angle data 9.2.2 In case of indefinite, free run, can not get one-rotation data 9.2.3 In case of rotation direction difference, 90° deviation or 180° deviation . 9.2.4 In case of rapid change in the output angle data and disturbance 9.3 If the situation does not improve  10. Electrical characteristics  10.1 Absolute maximum rating 10.2 Power-related characteristic 10.3 R/D conversion characteristic                                                                                                                                                                     | 68 69 71 72 73 74 75 76 77 77 78 78 79 -                                                                                                                                                                 |

| 9.1 In case of error detection 9.1.1 Suspicion of Abnormal Resolver Signal. 9.1.2 Suspicion of Disconnection Detection (DC-bias method) 9.1.3 Suspicion of Abnormal R/D conversion 9.2 In case of wrong angle data. 9.2.1 In case of fixed angle data 9.2.2 In case of indefinite, free run, can not get one-rotation data. 9.2.3 In case of rotation direction difference, 90° deviation or 180° deviation. 9.2.4 In case of rapid change in the output angle data and disturbance 9.3 If the situation does not improve.  10. Electrical characteristics 10.1 Absolute maximum rating 10.2 Power-related characteristic 10.3 R/D conversion characteristic 10.4 Built-In Self-Test(BIST) characteristic                                                                                                                       | 68 69 71 72 73 74 75 76 77 77 78 78 78 79 80 80                                                                                                                                                          |

| 9.1 In case of error detection 9.1.1 Suspicion of Abnormal Resolver Signal. 9.1.2 Suspicion of Disconnection Detection (DC-bias method) 9.1.3 Suspicion of Abnormal R/D conversion 9.2 In case of wrong angle data. 9.2.1 In case of fixed angle data 9.2.2 In case of indefinite, free run, can not get one-rotation data. 9.2.3 In case of rotation direction difference, 90° deviation or 180° deviation. 9.2.4 In case of rapid change in the output angle data and disturbance 9.3 If the situation does not improve.  10. Electrical characteristics 10.1 Absolute maximum rating 10.2 Power-related characteristic 10.3 R/D conversion characteristic 10.4 Built-In Self-Test(BIST) characteristic 10.5 Failure detection characteristic                                                                                 | 68 69 71 72 73 74 75 76 77 78 78 79 80 81 -                                                                                                                                                              |

| 9.1 In case of error detection 9.1.1 Suspicion of Abnormal Resolver Signal. 9.1.2 Suspicion of Disconnection Detection (DC-bias method) 9.1.3 Suspicion of Abnormal R/D conversion 9.2 In case of wrong angle data. 9.2.1 In case of fixed angle data 9.2.2 In case of indefinite, free run, can not get one-rotation data 9.2.3 In case of rotation direction difference, 90° deviation or 180° deviation 9.2.4 In case of rapid change in the output angle data and disturbance 9.3 If the situation does not improve  10. Electrical characteristics 10.1 Absolute maximum rating 10.2 Power-related characteristic 10.3 R/D conversion characteristic 10.4 Built-In Self-Test(BIST) characteristic 10.5 Failure detection characteristic 10.6 Analog signal characteristic                                                  | 68 69 71 72 73 75 76 77 77 78 78 78 79 80 81 82                                                                                                                                                          |

| 9.1 In case of error detection 9.1.1 Suspicion of Abnormal Resolver Signal. 9.1.2 Suspicion of Disconnection Detection (DC-bias method) 9.1.3 Suspicion of Abnormal R/D conversion 9.2 In case of wrong angle data. 9.2.1 In case of fixed angle data 9.2.2 In case of indefinite, free run, can not get one-rotation data. 9.2.3 In case of rotation direction difference, 90° deviation or 180° deviation. 9.2.4 In case of rapid change in the output angle data and disturbance. 9.3 If the situation does not improve.  10. Electrical characteristics 10.1 Absolute maximum rating. 10.2 Power-related characteristic. 10.3 R/D conversion characteristic 10.4 Built-In Self-Test(BIST) characteristic 10.5 Failure detection characteristic 10.6 Analog signal characteristics 10.7 DC characteristics of digital signal | 68 69 71 72 73 74 75 76 77 77 78 78 78 79 80 81 82 83 83                                                                                                                                                 |

| 9.1 In case of error detection 9.1.1 Suspicion of Abnormal Resolver Signal. 9.1.2 Suspicion of Disconnection Detection (DC-bias method) 9.1.3 Suspicion of Abnormal R/D conversion 9.2 In case of wrong angle data. 9.2.1 In case of fixed angle data 9.2.2 In case of indefinite, free run, can not get one-rotation data 9.2.3 In case of rotation direction difference, 90° deviation or 180° deviation 9.2.4 In case of rapid change in the output angle data and disturbance 9.3 If the situation does not improve  10. Electrical characteristics 10.1 Absolute maximum rating 10.2 Power-related characteristic 10.3 R/D conversion characteristic 10.4 Built-In Self-Test(BIST) characteristic 10.5 Failure detection characteristic 10.6 Analog signal characteristic                                                  | 68 69 71 72 73 74 75 76 77 78 78 78 78 80 81 83 83 -                                                                                                                                                     |

| 11. Appendix   |                          | – 🤉  | 90 -  |

|----------------|--------------------------|------|-------|

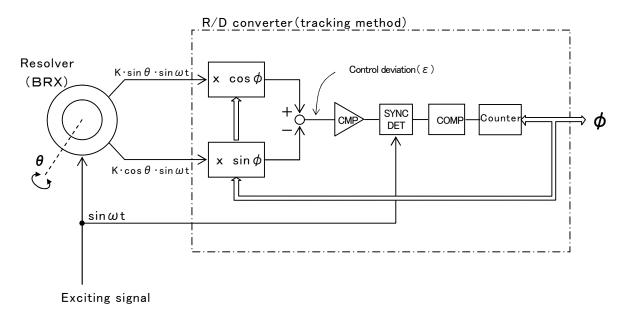

| 11.1 R/D conv  | version principle        |      | 90 -  |

| 11.2 About the | error of resolver system |      | 91 -  |

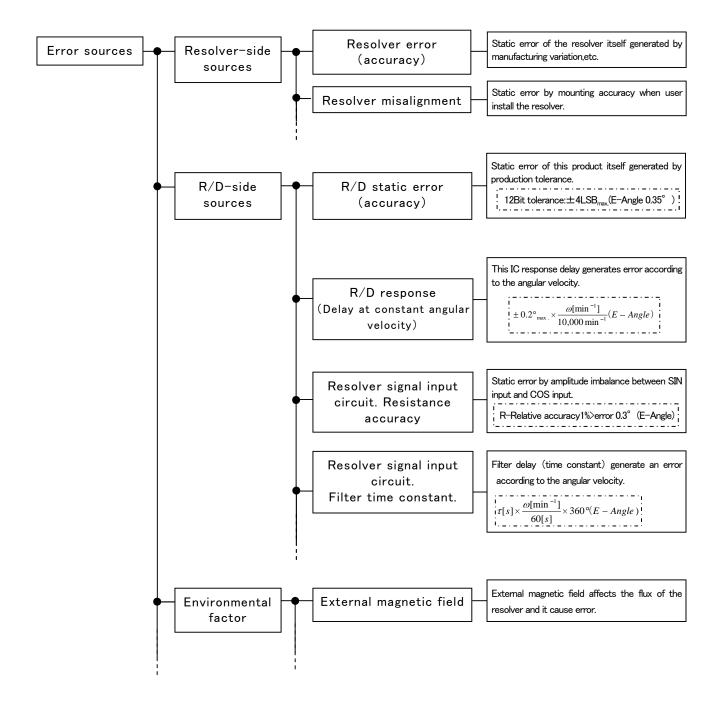

| 11.2.1 Error   | sources                  |      | 91 -  |

| 11.2.2 Error   | estimates                |      | 92 -  |

| 11.3 FAQ       |                          |      | 93 -  |

| 11.4 Terms and | Definitions              | 1    | 106 - |

| 12. Revision h | nistory                  | - 10 | 08 -  |

## Safety Precautions

fore use roder, please carefully read the specification and this manual for proper use. Incorrect usage do not operate normally, may damage the equipment that is connected to this product or this product.

Retain this manual, and please re-read when in doubt.

#### ■ Notes

Smartcoder (AU6805) is an integrated circuit (i.e electronic device) with a high grade quality level, but the predictable failure rate is not zero. Also there are some possibility to do unplanned work cause of noise, static electricity, wiring error, etc. The user is advised, therefore, that multiple safety means be incorporated in your system or product so as to prevent any consequential troubles resulting from the failure of our smartcoder (AU6805).

These application samples which listed in this manual are reference examples. If you use these examples, please make sure that you understand your system, equipments, and those functions and safety.

And the content written in this manual might be changed as needed. For the latest content, please contact your sales representative.

#### ■Product Warranty

#### (1) Warranty Period

The warranty period for Smartcoder (AU6805) is one year after shipping. Failed products within this warranty period will be replaced with new one.

#### (2)Coverage

Even if within the warranty period, we will not take responsibility for the products which show quality degradation caused by deviant usage against this document or specification like below.

- •In case of usage of unguaranteed condition/environment/handling nonlisted in this manual or specification.

- •In case of Remodeling/Repair which is not done by Tamagawa-seiki.

- •In case of misusing this product.

- In case of unforeseen matters which can not expect at technology level of shipping age

#### 1. Introduction

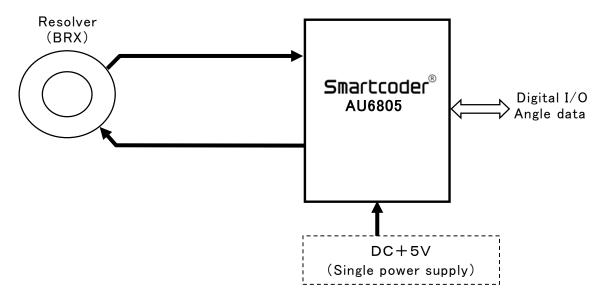

#### 1.1 Product Overview

Smartcoder (AU6805) is an R/D (Resolver to Digital) conversion IC used with a brushless Resolver (BRX) such as Singlsyn, Smartsyn, etc. It converts the electrical information (analog signal) corresponding to a mechanical rotational angle of the Resolver to the corresponding digital data and output it.

This IC applies a proven R/D conversion method "Digital Tracking Method", and be possible to provide a low- cost and many kind of angle detection applications while ensuring high reliability of resolver(syncro) system.

#### 1.2 Product Features

#### ■ Real time output

Max tracking rate :  $240,000 \text{min}^{-1}$  (Loop gain: fixed value setting) Max angular acceleration :  $1,000,000 \text{rad/s}^2$  (Loop gain: Auto tuning )

#### ■All-in-one design

Eliminates phase adjustment of exciting signal (allowable phase angle  $:\pm45^\circ$  while exciting signal 1 period is  $360^\circ$  ).

Implemented an Oscillator and excitation amplifier (current control type) help to reduce system cost.

#### ■ Small • Light weight

$7 \times 7$ mm (Pin pitch: 0.5mm, 48pin-LQFP, weight: 0.2g)

#### ■ Enhance error detection function

Followings are implemented. Abnormal Resolver Signal; Breaking of Resolver Signal Line; Abnormal R/D conversion; Abnormal High temperature inside IC.

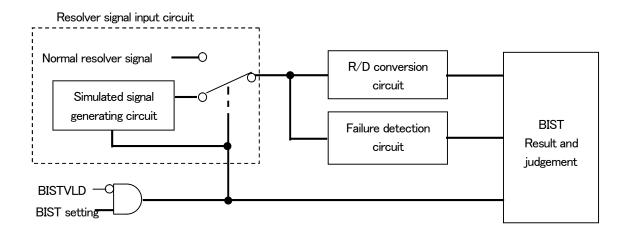

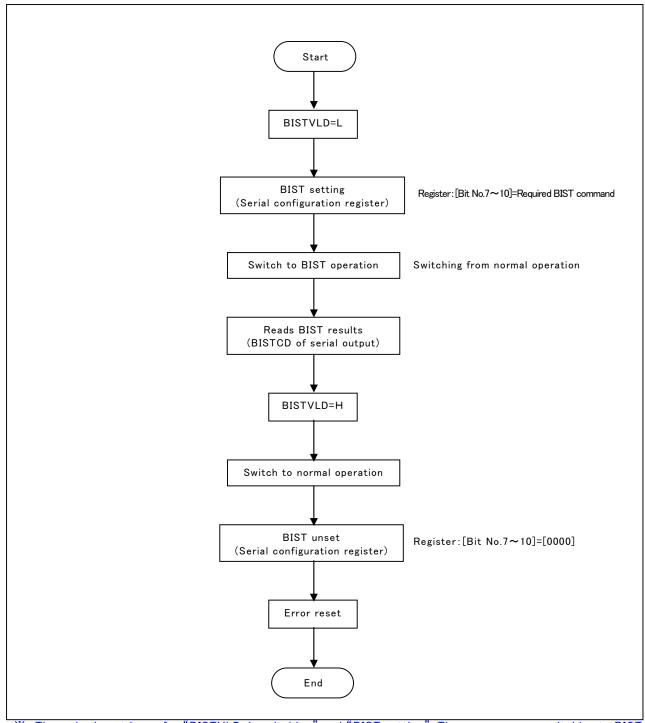

#### ■Implemented BIST(Built-In Self Test) function

R/D conversion function and breaking detection of signal line can be tested by themselves.

#### ■ Rich output form

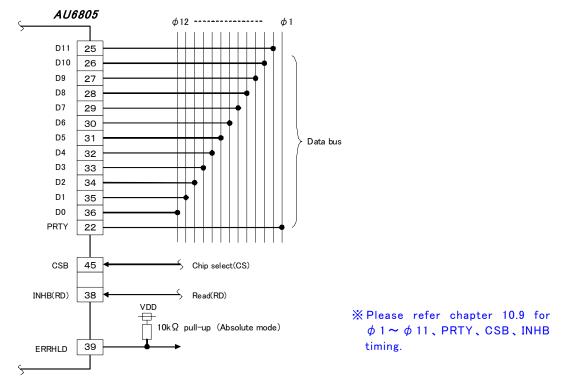

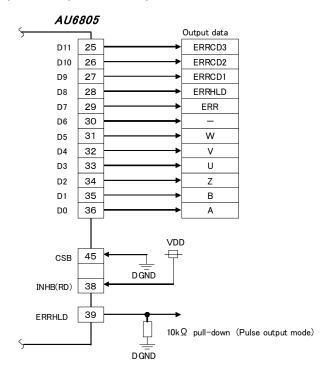

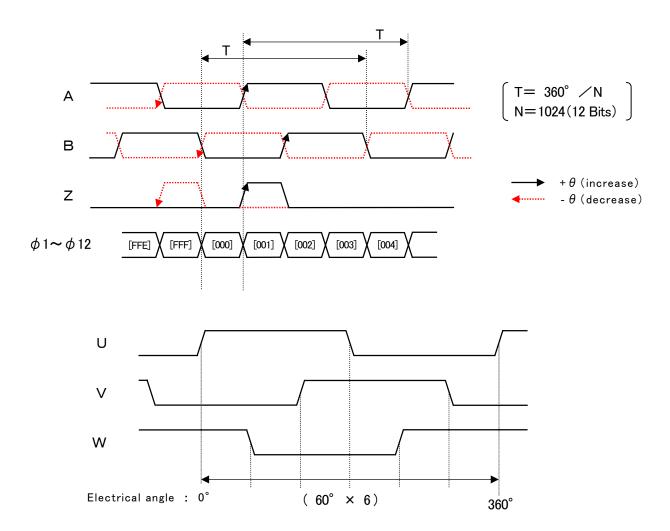

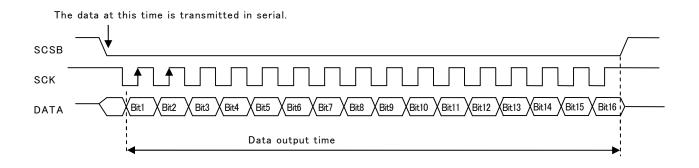

Binary-code Parallel 12bit Bus compatible, Positive logic + A,B,Z + Serial I/F

#### **■**DC+5V Single Power Supply

## 1.4 Spec Overview

| Ordered & Source                                      | Binary code parallel 12bit bus compatible, Positive logic                                                                                         |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Output form                                           | + A, B, Z + Serial I/F                                                                                                                            |

| Resolution                                            | 4,096 (2 <sup>12</sup> )                                                                                                                          |

| Conversion accuracy(Static)                           | ±4 LSB                                                                                                                                            |

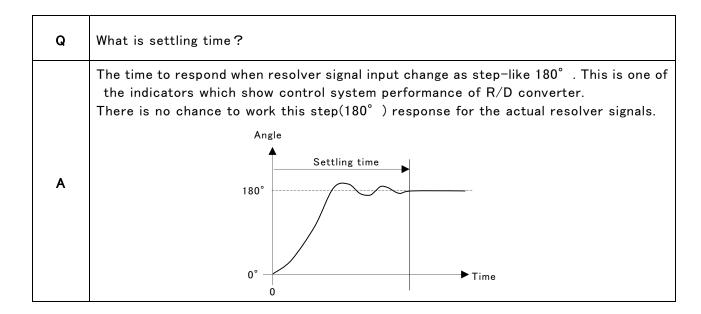

|                                                       | 42 ms typ. (Loop Gain Fixed Value setting (1) (Bandwidth 800Hz))                                                                                  |

|                                                       | 17 ms typ. (Loop Gain Fixed Value setting②(Bandwidth 2,000Hz))                                                                                    |

|                                                       | 14 ms typ. (Loop Gain Fixed Value setting③(Bandwidth 2,500Hz))                                                                                    |

| Settling time                                         | <b>24</b> ms typ. (Loop Gain Fixed Value setting (Bandwidth 1,500Hz))                                                                             |

| (Step input 180° in electric angle)                   | 35 ms typ. (Loop Gain Fixed Value setting (Bandwidth 1,000Hz))                                                                                    |

|                                                       | 69 ms typ. (Loop Gain Fixed Value setting⑥(Bandwidth 500Hz))                                                                                      |

|                                                       | 170 ms typ. (Loop Gain Fixed Value setting 🤊 (Bandwidth 200Hz))                                                                                   |

|                                                       | 1.5 ms typ. (Loop Gain Auto-tuning setting)                                                                                                       |

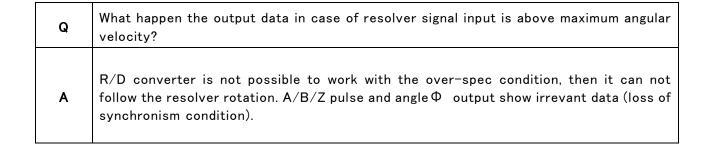

|                                                       | <b>240,000</b> min <sup>-1</sup> (Loop Gain Fixed Value setting)                                                                                  |

| Max. tracking rate                                    | 120,000 min <sup>-1</sup> (Loop Gain Auto-tuning setting)                                                                                         |

| Max. daorang raco                                     | 15,000 min <sup>-1</sup> (Loop Gain Fixed Value setting, Serial Absolute Output 16BIT setting)                                                    |

|                                                       | 12,000 min <sup>-1</sup> (Loop Gain Auto-tuning setting, Serial Absolute Output 16BIT setting)                                                    |

|                                                       | $\textbf{230,}000 \; \text{rad/s}^2 \; \text{typ.}  \text{(Loop Gain Fixed Value setting} \\ \textbf{1)}  (\text{Bandwidth} \; \; \text{800Hz}))$ |

|                                                       | 1,110,000 rad $\sim$ s <sup>2</sup> typ. (Loop Gain Fixed Value setting 2) (Bandwidth 2,000 Hz))                                                  |

|                                                       | 1,370,000 rad/s $^2$ typ. (Loop Gain Fixed Value setting $\Im$ (Bandwidth 2,500Hz))                                                               |

| Max. angular acceleration                             | 800,000 rad/s $^2$ typ. (Loop Gain Fixed Value setting $\textcircled{4}$ (Bandwidth 1,500Hz))                                                     |

| IVIAA. aligulai accelei auci i                        | <b>290,000</b> rad $\sqrt{s^2}$ typ. (Loop Gain Fixed Value setting § (Bandwidth 1,000 Hz))                                                       |

|                                                       | <b>70,000</b> rad $\sqrt{s^2}$ typ. (Loop Gain Fixed Value setting $\hat{\mathbb{G}}$ (Bandwidth 500Hz))                                          |

|                                                       | <b>7,000</b> rad $\sqrt{s^2}$ typ. (Loop Gain Fixed Value setting $\mathbb{T}(Bandwidth 200Hz)$ )                                                 |

|                                                       | 3,000,000 rad/s <sup>2</sup> typ. (Loop Gain Auto-tuning setting)                                                                                 |

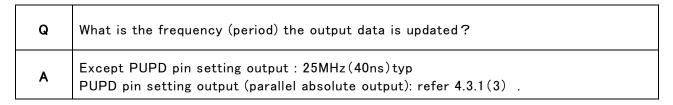

| Response (As output response delay in electric angle) | ±0.2° Max./10,000 min <sup>-1</sup>                                                                                                               |

| Encorder emulation output(A,B)                        | 1,024 C/T                                                                                                                                         |

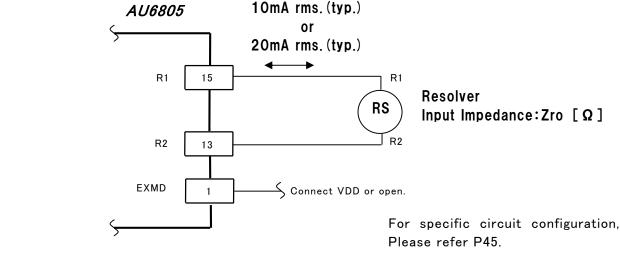

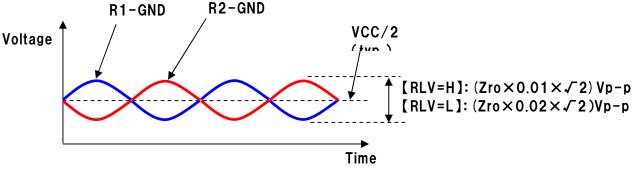

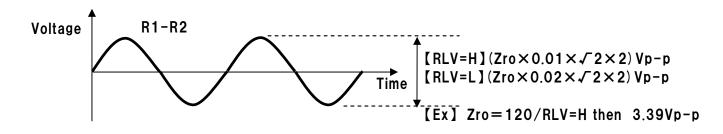

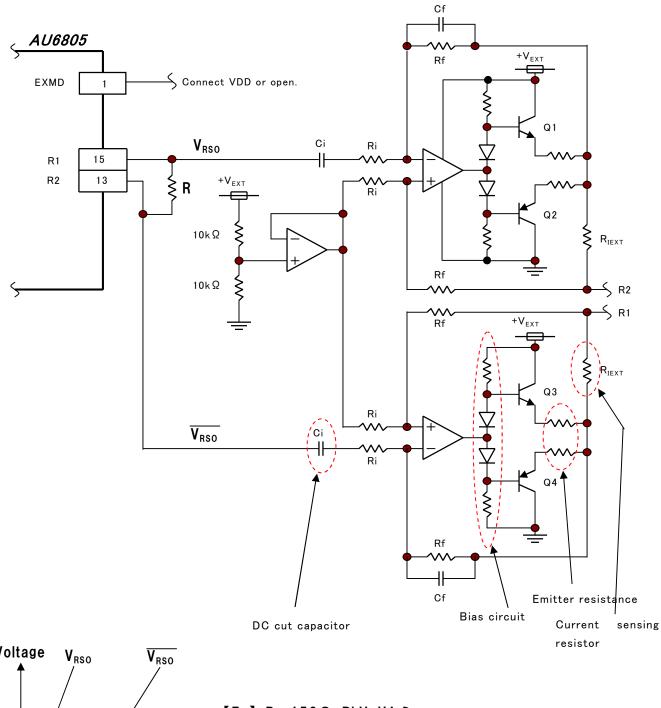

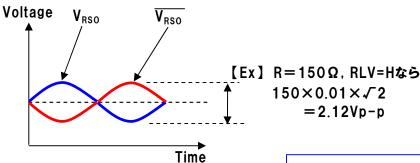

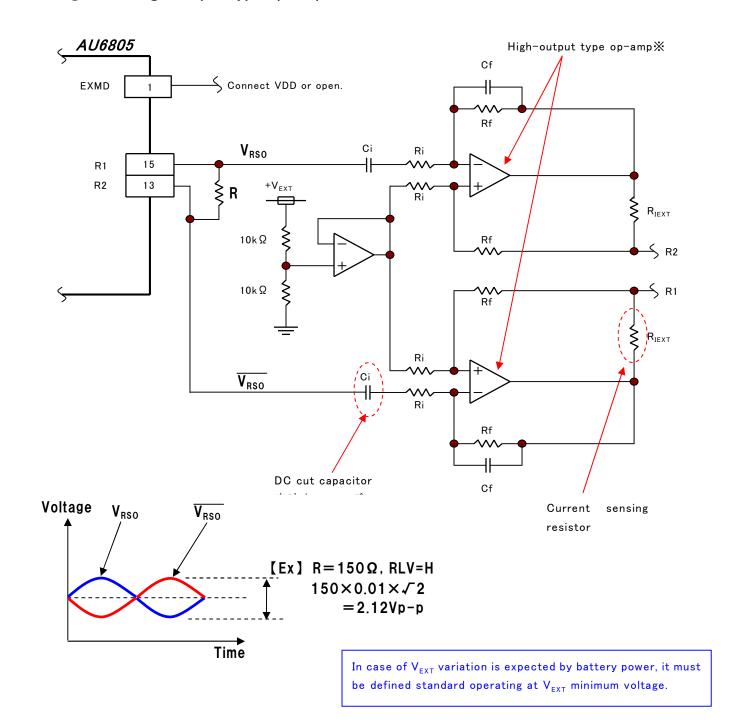

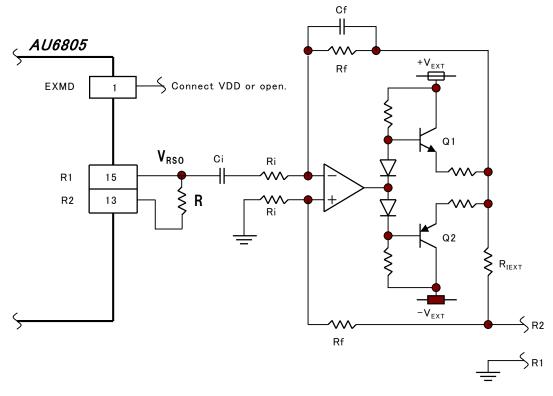

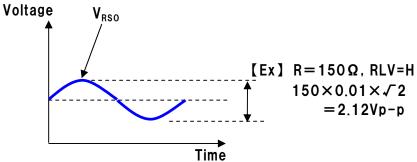

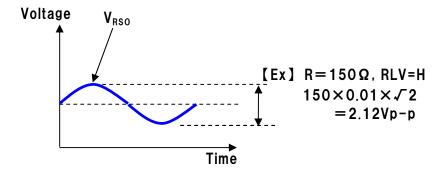

| Resolver excitation amplifier                         | 10mArms、10kHz typ. (RLV=H)                                                                                                                        |

| (current control type)                                | 20mArms、10kHz typ. (RLV=L)                                                                                                                        |

|                                                       | Abnormal resolver signal                                                                                                                          |

| Fault detection function                              | <ul><li>Breaking of resolver signal line</li><li>Abnormal R/D conversion</li></ul>                                                                |

|                                                       | • Abnormal high temperature inside IC                                                                                                             |

| BIST function                                         | BIST of R/D conversion (Test for R/D conversion)                                                                                                  |

| (BIST:Built-In Self Test)                             | BIST of signal failure (Test for signal failure )                                                                                                 |

|                                                       | DC 5V $\pm$ 10% 45mA max. (RLV=H)                                                                                                                 |

| Power source                                          | DC 5V $\pm$ 10% 65mA max. (RLV=L)                                                                                                                 |

| Operating temperature                                 | -40 ∼ +125°C (Do not exceed the Max. power consumption)                                                                                           |

| Storage temperature                                   | −65 ~ +150°C (before implementation)                                                                                                              |

| Package Thermal Resistance ( $R_{\theta JA}$ )        | $63.6^{\circ}$ /W (4-layer board: $76.2 \times 114.3 \times t1.6$ )                                                                               |

| Humidity                                              | 90% RH max. ( No condensation )                                                                                                                   |

| Mass                                                  | 0.2g typ.                                                                                                                                         |

#### 1.5 Related Documents

(1) SPC009574W00 Smartcoder (AU6805) Specificaion

## 2. Pin List (Name and Functions)

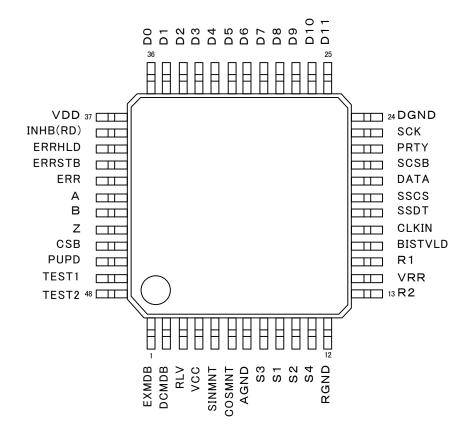

#### 2.1 Pin Assignment

参考図

## 2.2 Pin Description

| Pin No  | Symbol  | Class        | Description                                                                                                                                                                                                                                                                                                |                                                                           |                                                                    | Remarks chapter          |

|---------|---------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------|

|         |         |              | Input/Output mode selection p                                                                                                                                                                                                                                                                              | pin for R1,R2 (Pin13/Pin15).                                              |                                                                    |                          |

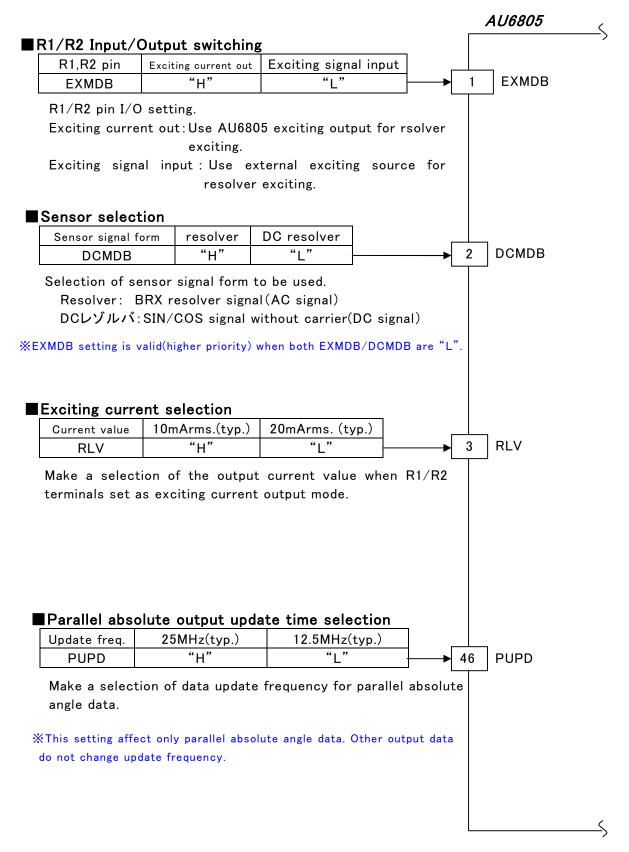

| 1       | EXMDB   | D/I          | R1,R2 I/O mode                                                                                                                                                                                                                                                                                             | Exciting current output                                                   | Exciting signal input                                              | (4.3.1(3))               |

|         |         |              | EXMDB                                                                                                                                                                                                                                                                                                      | H or Open                                                                 | L                                                                  |                          |

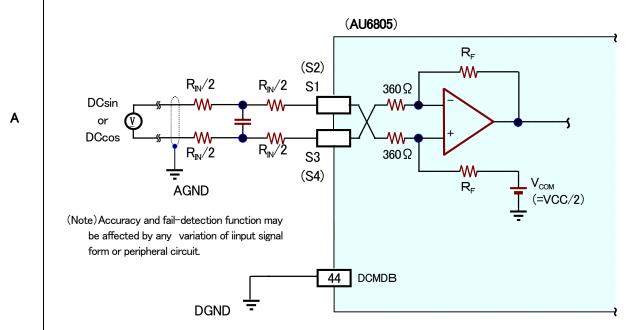

|         | 201122  | - A          | Sensor selection pin.                                                                                                                                                                                                                                                                                      |                                                                           |                                                                    | (40.4(0))                |

| 2 DCMDB |         | D/I          | Sensor                                                                                                                                                                                                                                                                                                     | Resolver                                                                  | DC Resolver(ex: Hall IC)                                           | (4.3.1(3))               |

|         |         |              | DCMDB  Current selection pin when Pin                                                                                                                                                                                                                                                                      | H or Open<br>n1(EXMDB) set as exciting current o                          | L L                                                                |                          |

| 3       | RLV     | D/I          | Exciting current                                                                                                                                                                                                                                                                                           | 10mArms.                                                                  | 20mArms.                                                           | (4.3.1(3))               |

|         |         | J, 1         | RLV                                                                                                                                                                                                                                                                                                        | H or Open                                                                 | ZOHIAMIS.                                                          | ( (, )                   |

| 4       | VCC     |              | Analog power pin. Connect to                                                                                                                                                                                                                                                                               | (4.4)                                                                     |                                                                    |                          |

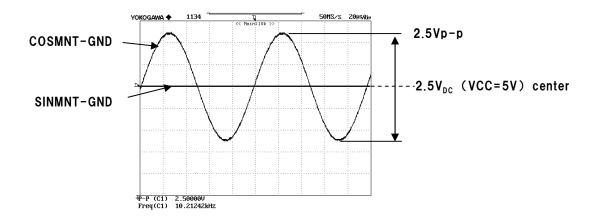

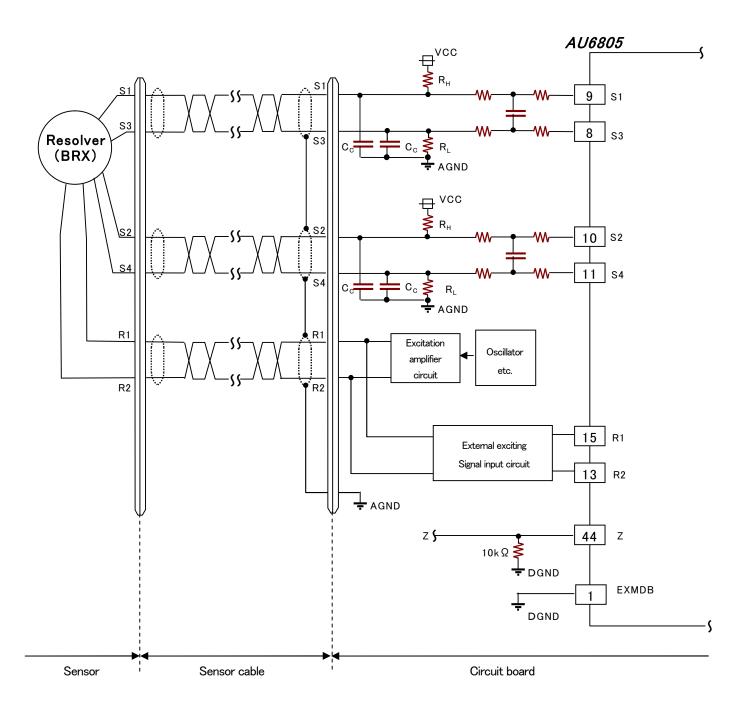

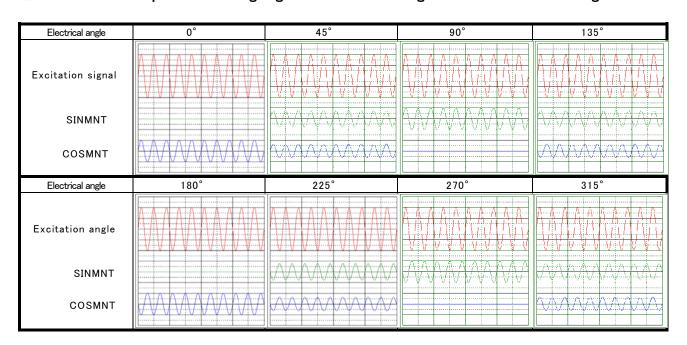

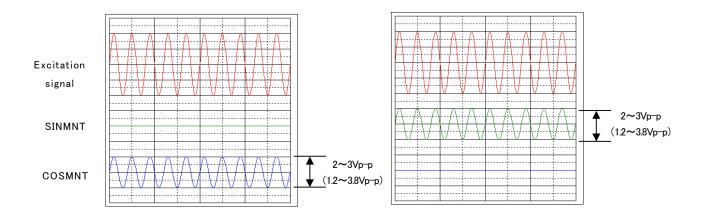

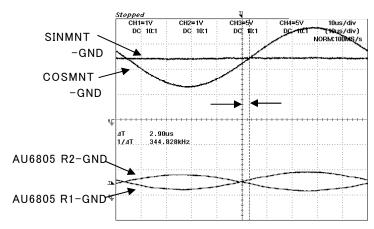

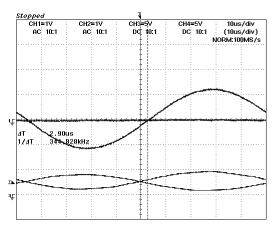

| 5       | SINMNT  | A/0          | Resolver signal (SIN) monitor of 2.5Vp-p for this pin.                                                                                                                                                                                                                                                     | output. Input gain should be adjusted                                     | by interface circuit to be approximately                           | (400)                    |

| 6       | COSMNT  | A/0          | Resolver signal (COS) moni approximately 2.5Vp-p for this                                                                                                                                                                                                                                                  |                                                                           | adjusted by interface circuit to be                                | (4.2.2)                  |

| 7       | AGND    |              | Analog ground pin. Connect to                                                                                                                                                                                                                                                                              | 0V.                                                                       |                                                                    | (4.4)                    |

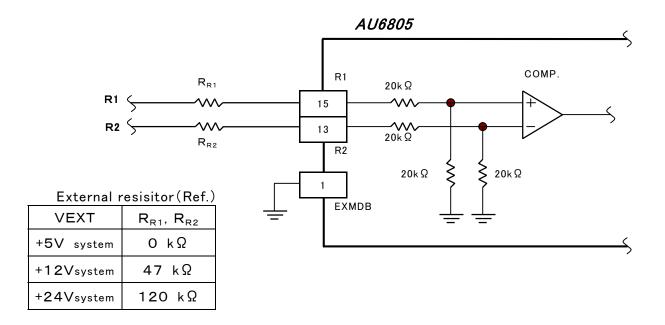

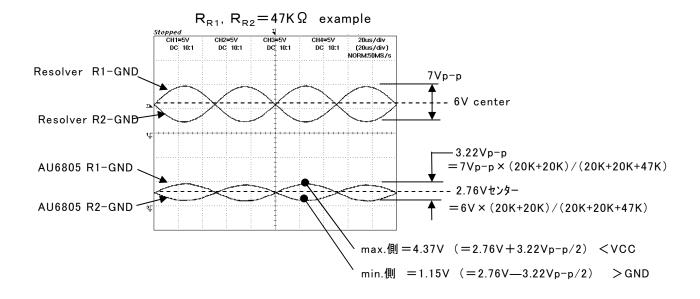

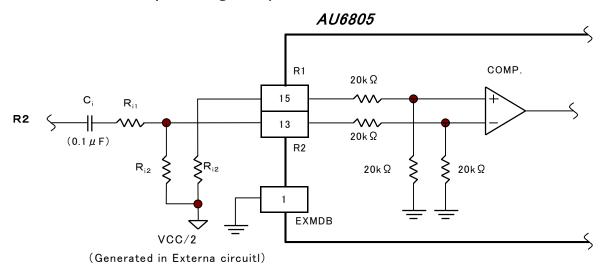

| 8       | S3      | A/I          | Resolver signal (S3) input pin. circuit.                                                                                                                                                                                                                                                                   | . This signal enters through the gain                                     | setting resistor of resolver signal input                          |                          |

| 9       | S1      | A⁄I          | circuit.                                                                                                                                                                                                                                                                                                   |                                                                           | setting resistor of resolver signal input                          | (4.2.2)                  |

| 10      | S2      | A⁄I          | circuit.                                                                                                                                                                                                                                                                                                   |                                                                           | setting resistor of resolver signal input                          | (/                       |

| 11      | S4      | A⁄I          | circuit.                                                                                                                                                                                                                                                                                                   |                                                                           | setting resistor of resolver signal input                          | (1.1)                    |

| 12      | RGND    |              | Exciting amplifier ground pin C                                                                                                                                                                                                                                                                            |                                                                           |                                                                    | (4.4)                    |

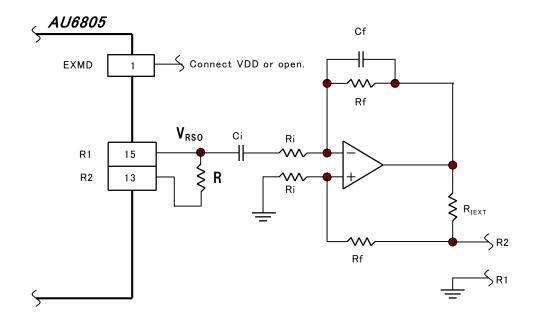

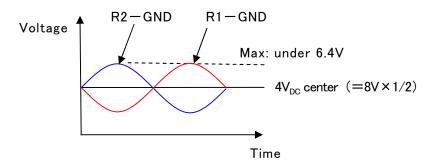

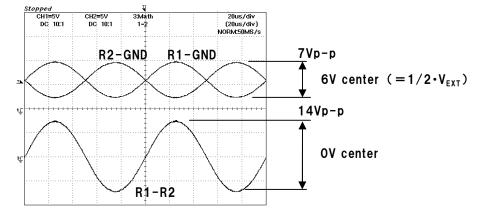

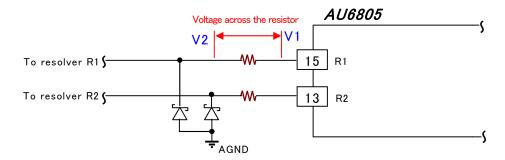

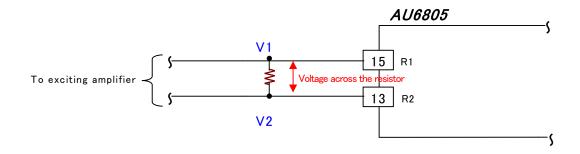

| 13      | R2      | A/O(I)       | Exciting signal(R2) I/O pin. Pin1(EXMDB) define I/O status. If set to output, sine-wave exciting current which can excite resolver directly generates between R1-R2 terminals. If set to input, input signal will be the resolver excitation signal that has been generated by an external oscillator, etc |                                                                           |                                                                    | (4.2.1)<br>(4.2.3)       |

| 14      | VRR     |              | Exciting amplifier power pin Connect to +5V.                                                                                                                                                                                                                                                               |                                                                           |                                                                    | (4.4)                    |

| 15      | R1      | A/O(I)       | Exciting signal(R1) I/O pin. Pir<br>which can excite resolver dire<br>the resolver excitation signal th                                                                                                                                                                                                    | (4.2.1)<br>(4.2.3)                                                        |                                                                    |                          |

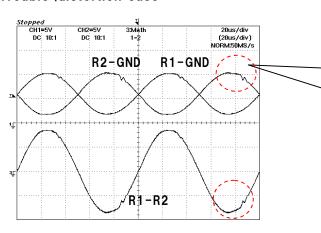

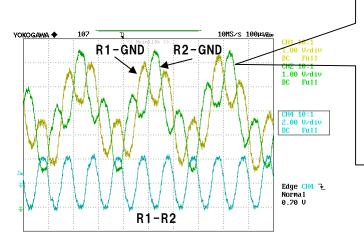

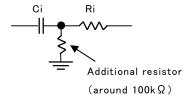

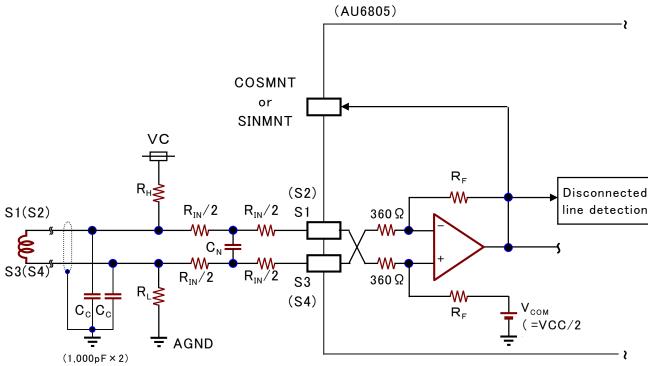

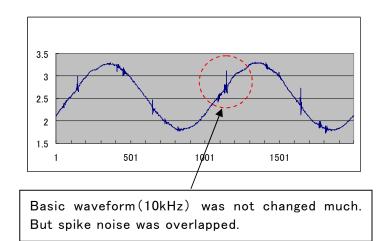

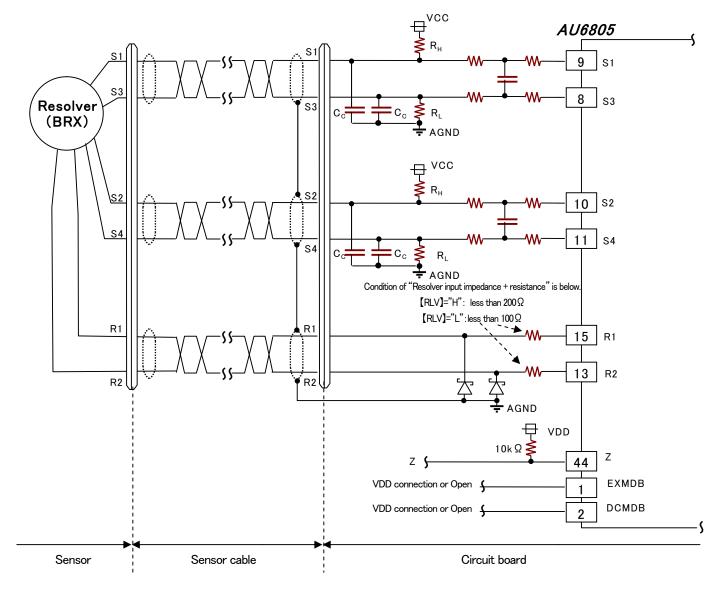

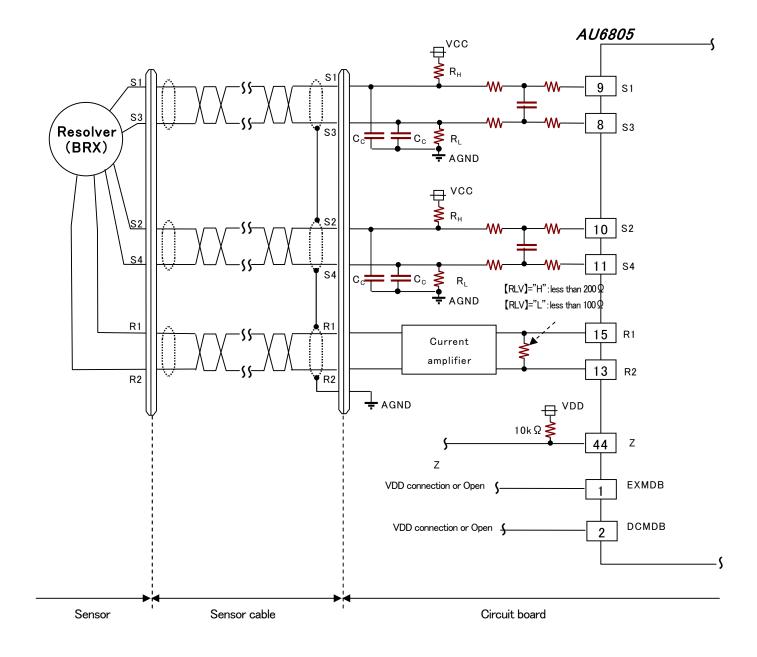

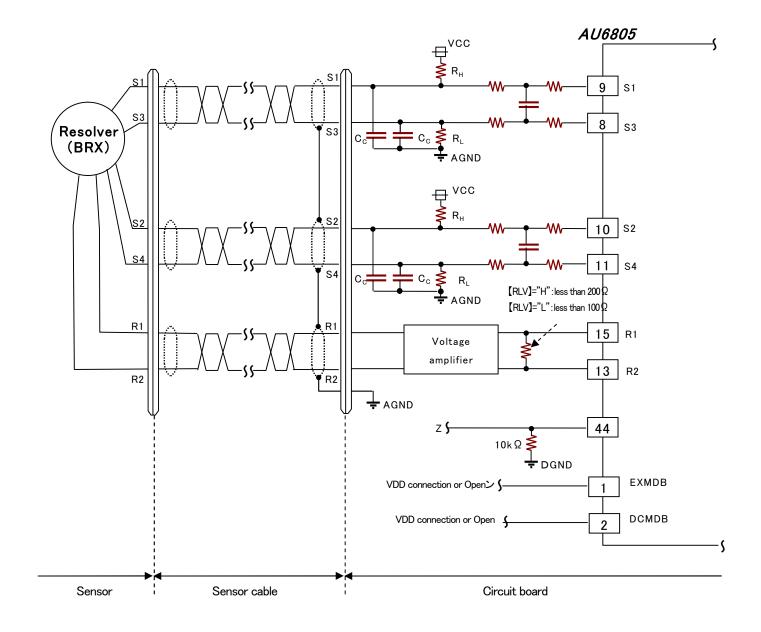

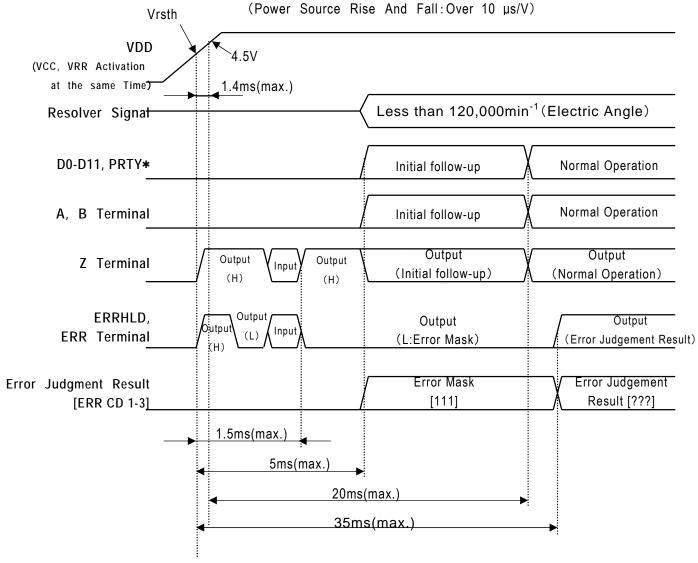

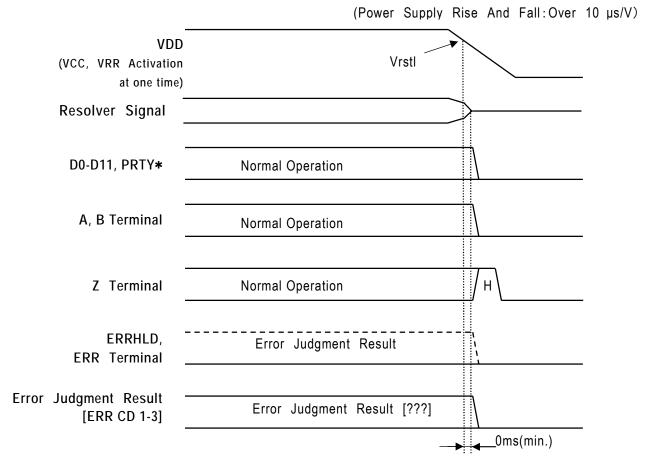

| 16      | BISTVLD | D/I          | BIST function control pin. BIST function can run when I code.                                                                                                                                                                                                                                              | (7)                                                                       |                                                                    |                          |